汽车、小型电动汽车 (EV) 、无绳工具和充电站对电源的要求越来越高,推动了向 48 V 电源系统的转变。这些系统的优点是效率高、损耗低、体积小和重量轻。所有这些电源系统将 48 V 总线提供的电源转换成可用电压,但需要使用电源转换器。

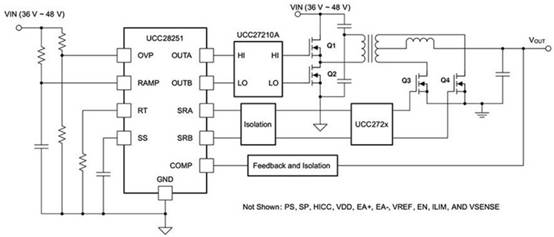

电源转换器使用开关电源技术,将 48 V 直流电转换为选定的电压。Texas Instruments 的 UCC28251PWR 便是这方面的一款典型 48 V 转换器,该器件基于半桥配置型电源开关器件,如场效应晶体管 (FET) ,如图 1 中的 Q1 和 Q2。这些器件通过脉冲宽度调制 (PWM) 控制器控制,以产生、调节所需的输出电压。

图 1:典型的 DC-DC 转换器使用 PWM 控制器驱动半桥配置型功率 FET。控制器调节 FET 输入端的脉冲宽度,以产生输出端的所需电压 (VOUT) 并进行调节。(图片来源:Texas Instruments)

在该电路中,场效应管 Q1 和 Q2 构成半桥拓扑结构。这两个受控器件交替导通,以驱动变压器。场效应管 Q3 和 Q4 是同步整流器,将变压器次级的开关波形转换为直流。同步整流器消除了与半导体整流器相关的串联压降,从而提高了效率。这些整流 FET 必须与初级电源开关器件同步驱动。

逆变器拓扑结构可以替代上述器件,这种结构包括由四个场效应管构成的全桥或“H”桥电路,或用于三相转换器的六个场效应管级联全电桥电路。所有这些技术都使用一对或多对功率器件。成对器件串连,就像图 1 中的场效应管。

但是,这些拓扑结构都存在两个关键问题。第一个问题是,决不允许高压侧 (Q1) 和低压侧 (Q2) 的开关器件同时导通。否则,48 V 总线和接地之间会出现短路。这种情况被称为击穿,并且通常会损坏电源开关。通过独立控制每个电源器件的开关时间,可以防止击穿。其目标是让激活器件在非激活器件导通之前关断。

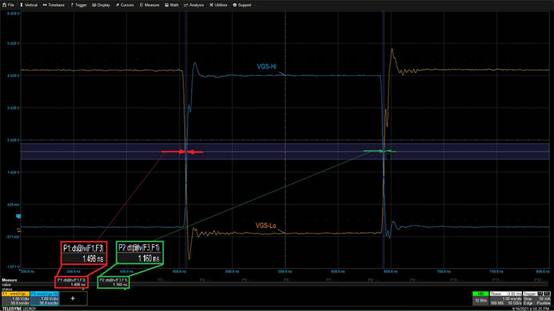

这两个事件(导通和关断)之间的延迟被称为初级空载时间。空载时间是通过比较在最大控制器脉冲宽度下,高压侧和低压侧 FET 的门极至源极电压 (VGS) 的转换时间来测量的(图 2) 。两组转换之间的延迟就是空载时间。

图 2:初级空载时间是通过比较在最大控制器脉冲宽度下、高压侧和低压侧 FET 的 VGS 转换时间来测量的。两组转换之间的延迟就是空载时间。在这个例子中,空载时间是1.498 ns 和 1.166 ns。(图片来源:Art Pini)

在图 2 中,低压侧 FET (VGS LO) 关断和高压侧 FET (VGS Hi) 导通之间的延迟是1.498 ns。另一种情况是,在高压侧场效应管关断和低压侧场效应管导通期间,延迟为 1.166 ns。如果这两个测量的延迟都为正,空载时间是可以接受的。注意,测量是在 PWM 控制器输出的最大脉宽下进行的。

在空载时间内,两个器件都没有导通;这就构成了“空载”损失。像所有损失一样,将其保持在最低限度变得越来越重要。

第二个关键问题是协调同步整流器的工作和初级开关动作。

图 1 所示的 UCC28251PWR 控制器可以控制半桥或全桥电路,并提供栅极驱动信号和具有可设置延迟的同步整流器输出。UCC28251PWR 控制初级侧的空载时间,还包括逐周期过流保护。初级输出和次级同步整流器驱动信号之间的延迟(称为初级空载时间)可通过两个外部电阻器单独设置。

PWM 控制器搭配使用初级侧半桥栅极驱动 IC――Texas Instruments UCC27210DDAR。这款 IC 驱动半桥配置中的两个 N 沟道 FET 的栅源级输入。由于自身的固有传播延迟,即 18 ns(典型值),该器件会影响初级侧的空载时间。通过匹配两个栅极驱动输出之间的延迟,可以将传播延迟问题最小化。UCC27210DDAR 栅极驱动器 IC 的输出在 2ns 内完成匹配。具有类似时序特性的同系列栅极驱动器用来驱动同步整流 FET。

总结

迁移到 48 V 系统在效率、尺寸和重量方面具有天然优势,但设计者需要了解空载时间原因以及如何将其降至最小。如图所示,特种 IC 具有保障 48 V 电源转换器正常工作的必要功能。这类 IC 控制初级和次级空载时间,消除了半桥和全桥电路拓扑结构中可能存在的主要问题。