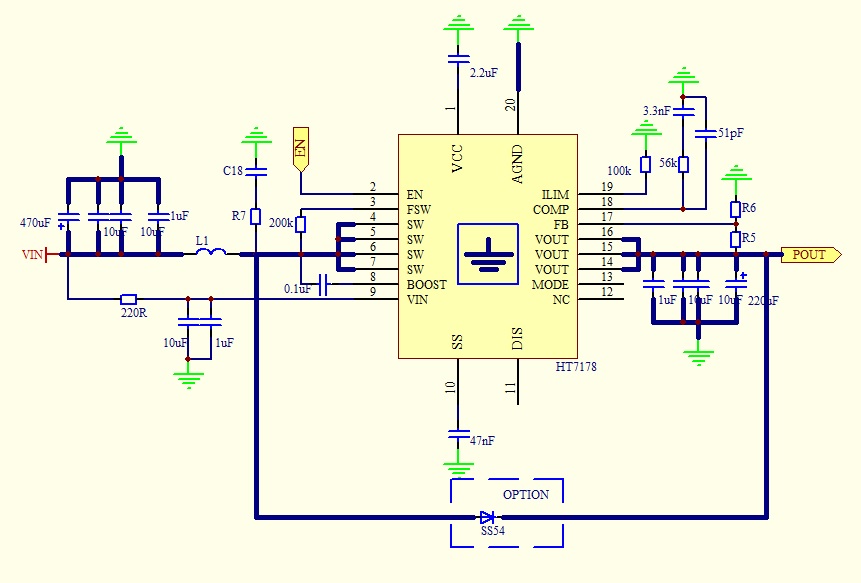

此文档适用于HT7178、HT7167、HT7166、HT71678

HT7178为20V/14A 同步升压IC;

HT7167、HT7166为13V/12A同步升压IC;

HT71678为带音频检测的13V/12A同步升压IC;

我们知道,同步升压IC,内置一个功率开关管和一个同步整流管,由于HT 产品均为大电流升压,电感峰值电流>10A,在两个功率管交替打开的时候,会在SW、POUT上产生高的毛刺。电感电流越大,电压毛刺越大。不合理的布局,导致EMI辐射超标,DCDC转换效率变低,IC可靠性降低。

下面以HT7178 为例,阐述如何进行合理LAYOUT。

1 输入滤波电容:为防止大电流工作时,VIN 输入波动大导致系统欠压,建议输入增加470uF电解电容。

2 输出滤波电容:原则上,小电容能靠多近VOUT 管脚就靠多近,且电容地与芯片底部地回路粗短;大电容完全滤除电压毛刺后再供给后级。

3 图中粗线为功率回路,尽量保持大电流路径足够线宽,且此块地平面能完整,回路最短(地包括VIN 输入的地,输入滤波电容的地,芯片底部地,输出滤波电容地)。

4 电感L1 选择:1.5uH or 2.2uH,饱和电流>12A;建议择2.2uH 1040封装一体成型电感,Isat=16A 。

5 开关工作频率:开关频率高,开关损耗大,但输入电流纹波小,折中这两个考虑,一般DCDC开关频率在500kHz―800kHz之间;200k 电阻对应650kHz开关频率。

6 输入RC 滤波:在单节应用时,RC滤波防止VIN 波动大造成HT7178欠压;VIN大于8V应用时,增加R来保护HT7178的9脚VIN的正常工作。

7 SW 增加RC,吸收SW 开关时候的毛刺,削减辐射

8 R5、R6决定升压;ILIM决定输入峰值限流:COMP为补偿网络,须根据实际应用合理计算。

9 预留二极管SS54,可提高DCDC 转换效率

下面以实际测试为例,阐述各参数的影响,主要针对SW、POUT上的毛刺,以及效率做说明。

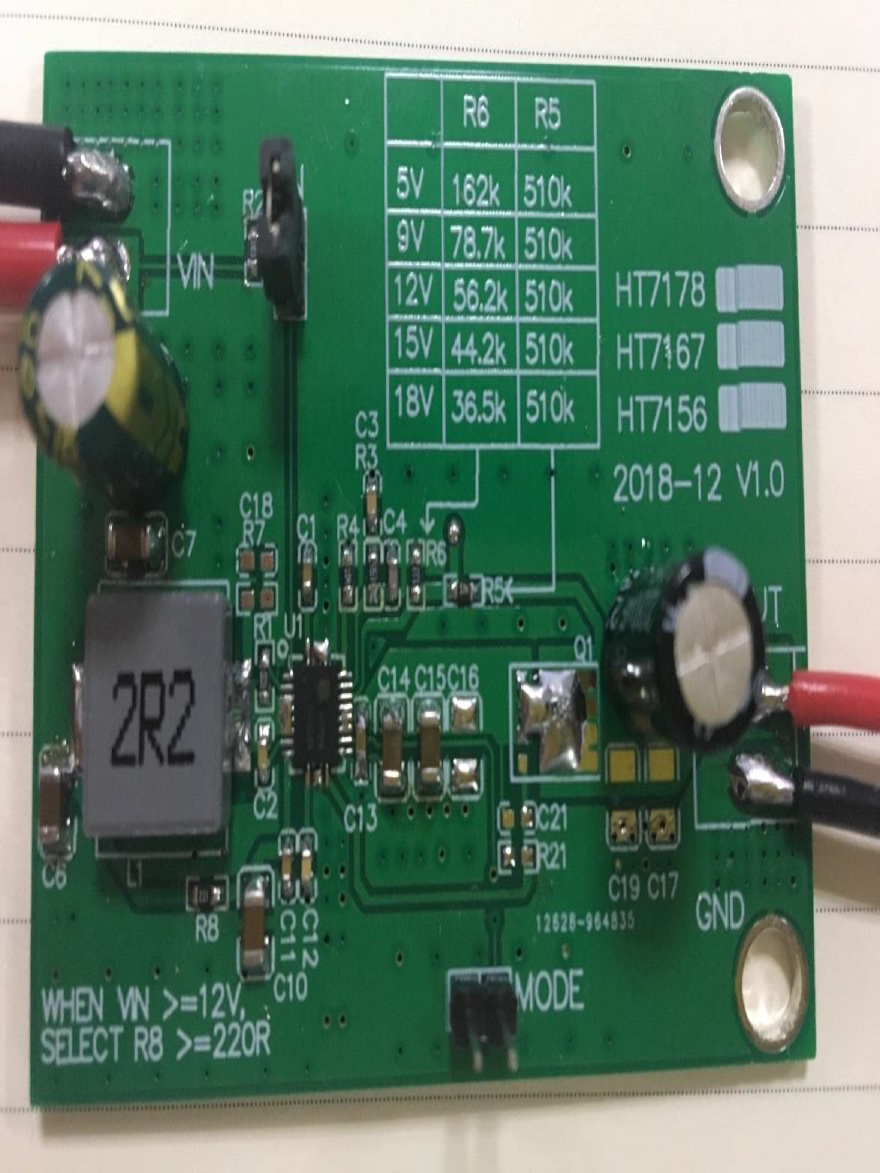

测试对比原型如下图:

条件:输入3.7V, 输入滤波470uF+2*10uF;限流电阻100k,限流12A peak;

输出13.2V(510k+51k);输出滤波220uF+2*10uF+1uF; COMP=(56k+3.3nF)// 51pF;

SW无RC;无预留二极管SS54;

负载:2A直流负载输出;

1 测试结果:输入3.7V,电流8.33A,输出13.28V 2A,效率86.17%

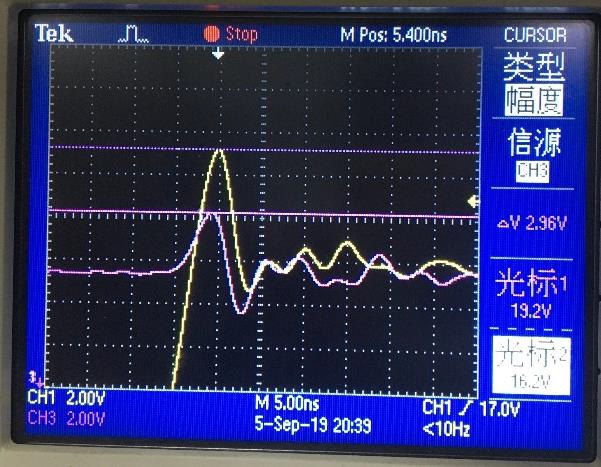

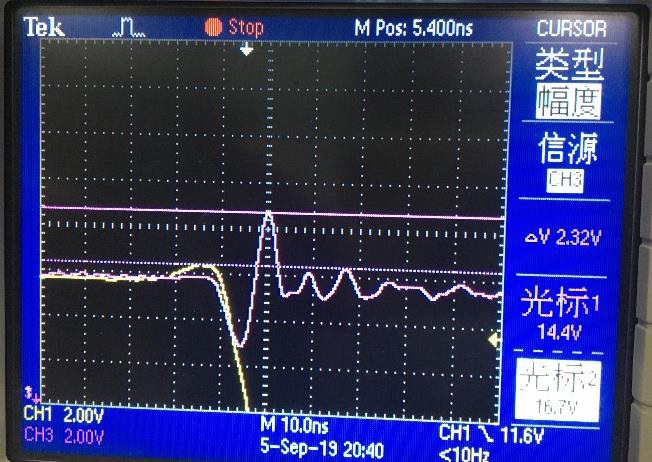

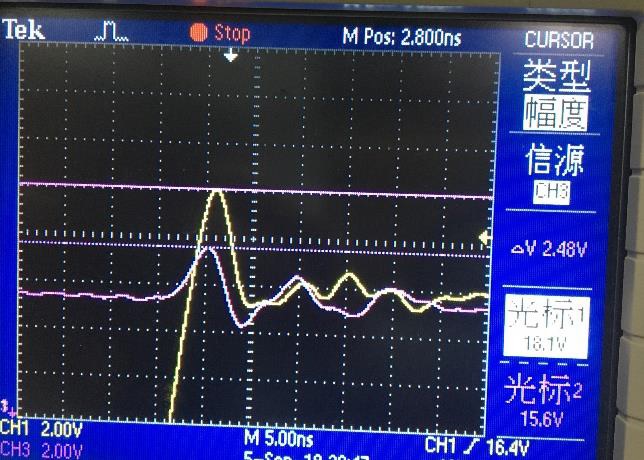

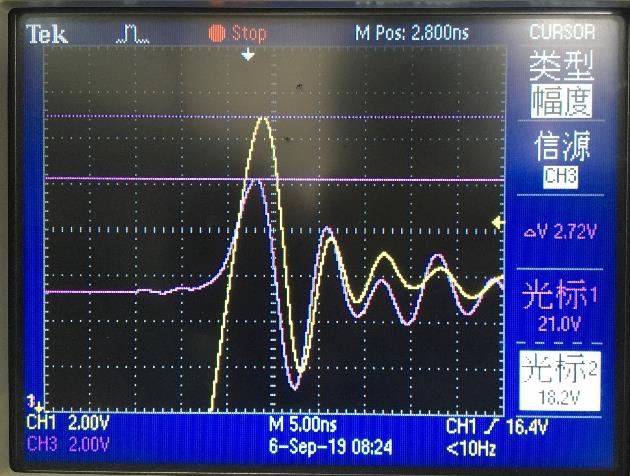

SW 上升沿,下管关,整流管开

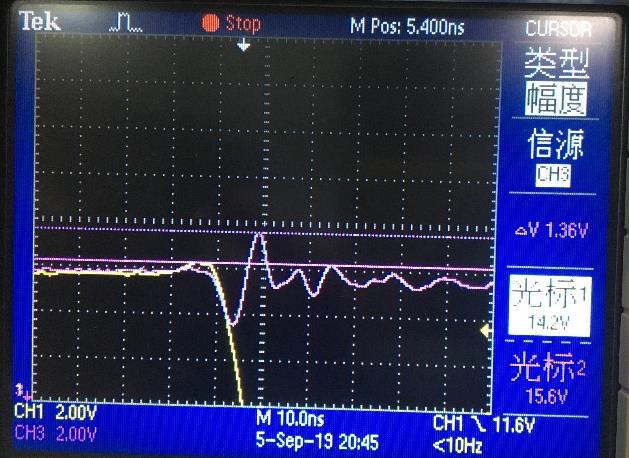

SW下降沿,下管开,整流管关

黄色为SW 管脚波形;红色为POUT波形;测试均为靠近芯片管脚,下同;

可以看到,SW上升沿,在SW上有很高的毛刺,达到了惊人的19.2V,POUT上为16.2V;

SW下降沿,SW 死区毛刺较小,但POUT上有更高的16.7V毛刺;

2 在SW与POUT 直接,并联肖特基二极管SS52;二极管压降约0.2V,当整流管电流大于10A 时,整流管电压会大于0.2V,这时候SS52 可分担部分电流;同时,在下管和整流管交替打开时候,由于死区时间,靠内部体二极管续流,这样SS52 可很好续流。

输入3.7V,电流8.18A,输出13.26V 2A,效率87.62%,提升约1.5点效率

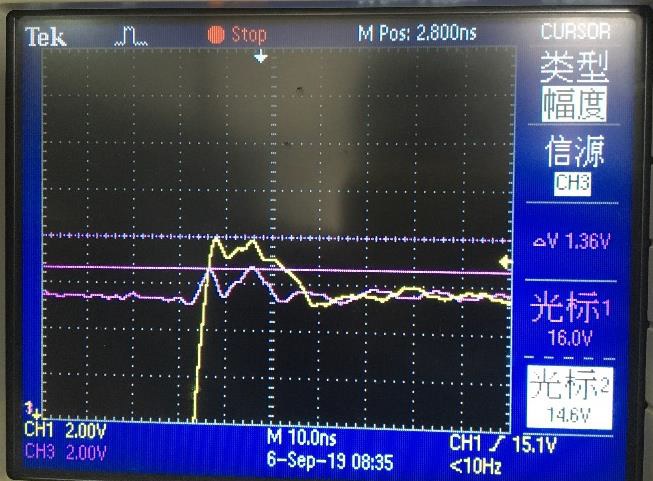

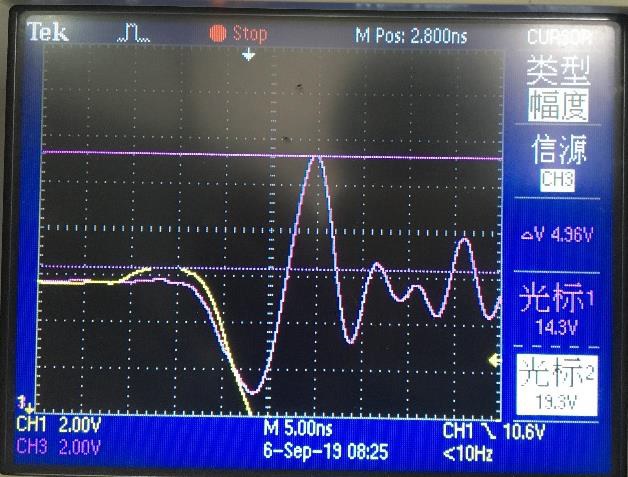

SW 上升沿,下管关,整流管开

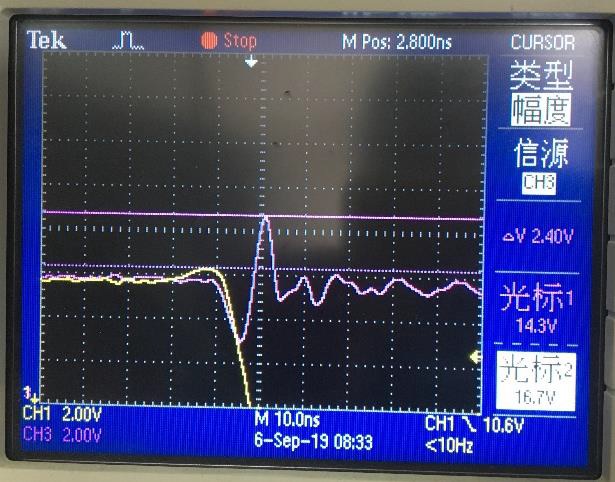

SW 下降沿,下管开,整流管关

SW 上升沿,在SW 上有18.1V,POUT 上为15.6V;--SW 小了1V,POUT 小了0.5V;

SW 下降沿,SW 死区毛刺较小,POUT 上为15.6V;--POUT 小了1V;

可以看到了,在SW 和POUT 之间并了一个SS52,增加了一路续流路径,SW 和POUT 的毛刺有明显减小,尤其是POUT 在整流管关的时候;

3 SW 上加RC,1Ω+3.3nF

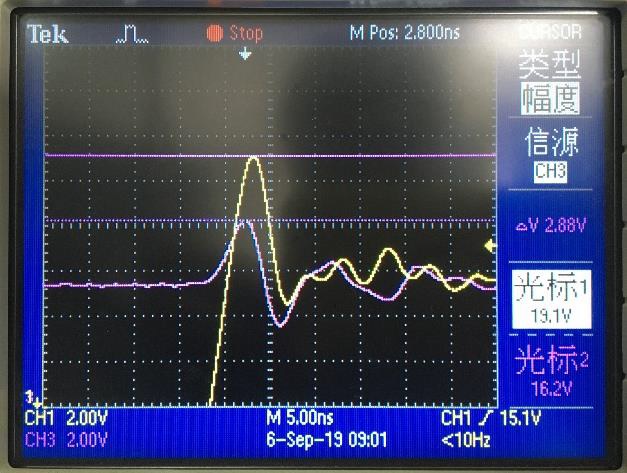

SW 上升沿,下管关,整流管开

SW 下降沿,下管开,整流管关

SW 上升沿,在SW 上只有16V,POUT 上为14.6V;--SW 小了近3V,POUT 小了1.5V;

SW 下降沿,SW 死区毛刺较小,POUT 上仍为16.7V;--维持不变;

在SW 上加了RC,延缓了SW 开关的上升沿、下降沿;可以看到,在SW 上升的时候,毛刺明显变小,且震荡也变很小,对于改善EMI 有很好的帮助;但是,在整流管关的时候,对于POUT 上的毛刺作用不大。

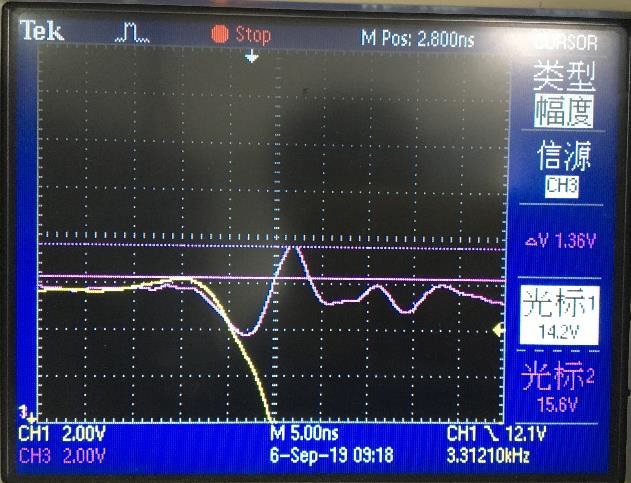

4 POUTPOUT上挨近管脚的上挨近管脚的11uFuF电容去掉电容去掉

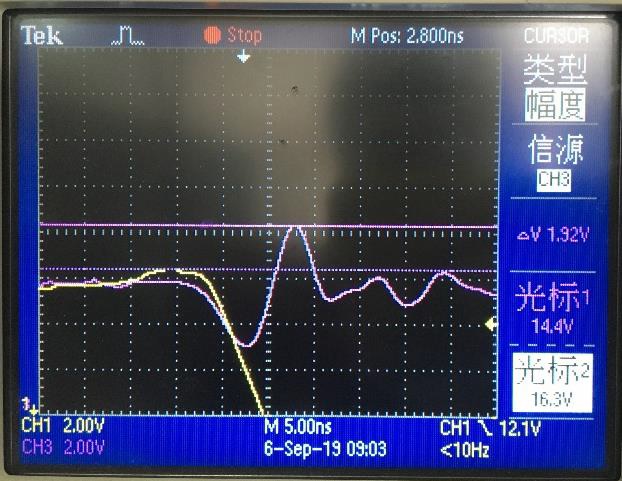

SW上升沿,下管关,整流管开

SW下降沿,下管开,整流管关

SW上升沿,在上升沿,在SW上有上有21V,POUT上为上为18.2V;;----SW大了近2V,,POUT大了2V;;

SW下降沿,SW死区毛刺较小,POUT上为19.3V;----POUT大了2.5V;

可以看到,在挨近POUT管脚,无11uFuF电容的情况下,情况都有明显恶化,此种情况极易造成芯片损伤;另外,SW、POUT端的震荡也加剧,辐射变严重。

5 POUT上挨近管脚的上1uF电容上再并上0603封装10uF电容

SW上升沿,下管关,整流管开

SW下降沿,下管开,整流管关

SW上升沿,在上升沿,在SW上有19.1V,POUT上为16.2V;----无明显变化

SW下降沿,SW死区毛刺较小,POUT上有上有16.3V;----略微降低0.4V

在POUT上继续增大滤波电容,对于SW端基本上没有再改善;对于POUT本身,有稍微改善。

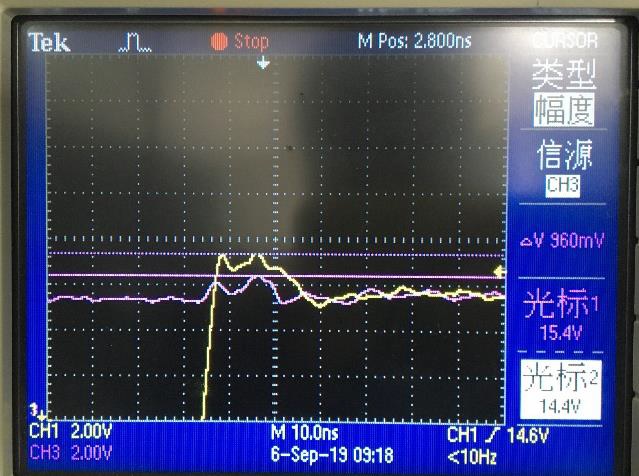

6 在结合上述,在SW加RC(1Ω+3.3nF),SW与POUT之间加SS52

SW上升沿,下管关,整流管开

SW下降沿,下管开,整流管关

SW在上升沿,在SW上有15.4V,POUT上为14.4V;----SW小了3.8V,POUT小了小了1.8V;

SW下降沿,SW死区毛刺较小,POUT上为15.6V;----POUT小了1V;

综合来看,SW加上RC,能有效改善SW端的毛刺,降幅很明显;

POUT上,滤波小电容的挨近管脚,能有效减小POUT端的毛刺。

SW与POUT之间,并联SS52,可以进一步降低两者的毛刺。

上述测试前提是在地平面完整的情况下进行测试;若地分割严重,电流回路路径长,地阻抗大,也会进一步恶化情况。

PCB LAYOUT布局,请保持VIN进来的地,VIN滤波电容的地,芯片底部的地,POUT上滤波电容的地,为一个完整的平面。