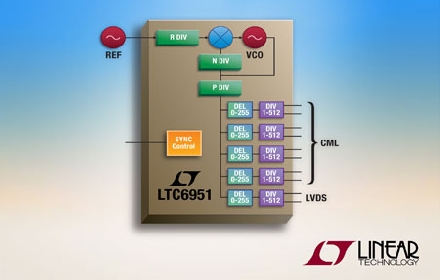

Linear推出低相位噪声整数N合成器LTC6951,该器件集成了 VCO 和超低抖动时钟分配电路,非常适合为数据转换器提供时钟。LTC6951 提供 4 个高性能电流模式逻辑 (CML) 输出,每个输出都配备了一个独立的低噪声时钟分频器和数字延迟构件,以涵盖从 1.95MHz 到 2700MHz 的宽频率范围。当以高输入频率和快速输出数据传送速率为数据转换器提供时钟时,凭借总的115fsRMS绝对抖动 (SNR 方法),LTC6951 可提供实现最佳 SNR 所必需的低抖动时钟。

LTC6951 引入了 3 种智能方法,以简化输出时钟扩展和大型时钟树的建立,具多个子板卡或大量数据转换器的系统会用到大型时钟树。凌力尔特专有的EZSync™输出同步方法可确保,在 LTC6951和伴随的EZSync支持性器件的所有时钟分频器输出之间,保持可重复和确定性的相位关系。ParallelSync™多芯片并联同步功能允许按照公共基准时钟对多个 LTC6951 IC 的输出重新定时。这就允许在基准时钟域与基准一致的同步,并易于满足毫微秒范围设置和保持时间要求。符合 JESD204B 子类 1 要求的 EZ204Sync™同步方法是在之前两种方法的基础上开发的,可用来跨多个并联的 LTC6951 IC 以及其他任何EZSync兼容时钟器件,产生对这一 JEDEC 标准必不可少的 SYSREF 和 DEVCLK 信号。

运用 LTC6951Wizard™仿真和设计工具,可以非常简便地用 LTC6951 进行设计,该工具可在www.linear.com.cn/LTC6951Wizard免费下载。只需点击一下按钮,LTC6951Wizard 软件就可提供恰当的 PLL 设置和环路滤波器组件值,并准确地预测个别输出的相位噪声和抖动。除了性能仿真,LTC6951Wizard GUI 还提供一条示波器曲线,以基于时钟分频器、延迟和同步设置,仿真 LTC6951 输出的时域结果,从而简化了设计过程,并能够在电路调试阶段提供帮助。

LTC6951 在−40°C 至 105°C的整个工作结温范围内进行了规定。该器件采用节省空间的 5mm x 7mm、40 引线塑料 QFN 封装。LTC6951 的千片批购价为每片8.75美元,已开始供货。

照片说明:集成了 VCO 时钟分配电路的超低抖动时钟合成器

性能概要:LTC6951

・ 集成了 VCO 的低噪声整数 N PLL

・ 90fsRMS输出抖动 (12kHz 至 20MHz)

・ 115fsRMS输出抖动 (ADC SNR 方法)

・ 噪声层输出抖动 = −165dBc/Hz (在 250MHz)

・ EZSync多芯片时钟边沿同步

・ 产生符合 JESD204B 子类 1 要求的 SYSREF 信号

・ 1.95MHz 至 2.5GHz 输出频率 (LTC6951)

・ 2.1MHz 至 2.7GHz 输出频率 (LTC6951-1)

・ −229dBc/Hz归一化带内相位噪声层

・ −277dBc/Hz归一化带内 1/f 噪声

・ 5 个独立的低噪声输出

・ 5 个独立的可编程分频器和延迟

・ 提供LTC6951Wizard 软件设计工具支持