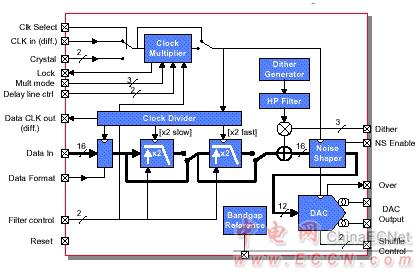

The Fujitsu MB86060 is a high performance 12-bit, 400MSa/s Digital-to-Analog Converter (DAC) enhanced with a 16-bit interpolation filtering front-end. Use of novel techniques for the converter architecture delivers high speed operation consistent with BiCMOS or bipolar devices but at the low power of CMOS. Fujitsu’s proprietary architecture is the subject of several patent applications. Additional versatility is provided by selectable input interpolation filters, programmable dither and noise shaping facilities. Excellent SFDR performance coupled with high speed conversion rate and low power make this device particularly suitable for high performance communication systems, in particular direct IF synthesis applications.

Features

16-bit Interpolating Digital to Analog conversion x1, x2 or x4 interpolation filtering 100MSa/s input, with x4 interpolation enabled Programmable highpass filtered dither Selectable 2nd order noise shaping Versatile CMOS digital interface Internal programmable clock multiplier Low power, 3.3V operation (343mW @32MSa/s input, x4) Performance enhanced pinout with on-chip decoupling 0.35µm CMOS technology with Triple Well Industrial temperature range (-40°C to +85°C)

Applications

Direct IF Synthesis Cellular basestations Wide-band communications systems

Functional Description

The MB86060 integrates a 12-bit 400MSa/s DAC with selectable front end processing to provide input interpolation filtering, dither and noise shaping. Versatile interfacing via the 16-bit parallel CMOS data input allows different system requirements to be accommodated, with either offset binary or 2’s complement data formats selected by an input format control. The device is manufactured in a 0.35µm advanced CMOS process with Triple Well extension giving improved isolation between analog blocks and digital-analog.